# **ISL35111 Evaluation Board User Guide**

### **Table of Contents**

| Introduction to the ISL35111DRZ-EVALZ Evaluation Kit |   |

|------------------------------------------------------|---|

| Operation of the ISL35111 Evaluation Board           | 2 |

| Power Supply                                         |   |

| High Speed Data I/O Interface Connectors             | 2 |

| Output De-Emphasis Control                           | 2 |

| Transmit Disable                                     | 3 |

| Baseline Performance                                 | 3 |

| Schematic                                            | 4 |

### Introduction to the ISL35111DRZ-EVALZ Evaluation Kit

The ISL35111 Evaluation Board is a versatile stand-alone printed circuit board developed to evaluate the performance of the Intersil ISL35111 driver.

The evaluation kit includes:

- ISL35111 evaluation board

- Power cable

The key features of the Evaluation board are:

- ISL35111 IC

- Connection to external 3.3V power supply.

- On board DC/DC converter that provides the 1.2V supply to the IC.

- On board de-emphasis control through a set of headers.

- SMA connectors to access differential input and output.

### Operation of the ISL35111 Evaluation Board

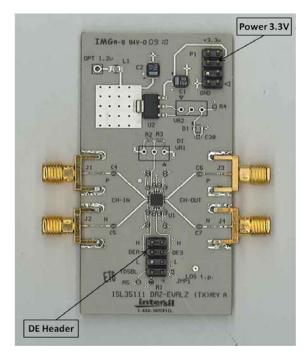

This section describes how to simply setup your ISL35111 evaluation board making sure proper power is applied, describing connection to high speed RF input and output and finally describing how to easily set the de-emphasis level. The board is shown in Figure 1.

FIGURE 1. ISL35111 EVALUATION BOARD

#### **Power Supply**

The board needs to be powered by an independent external 3.3V power supply via the power header located at the top of the board using the power cable provided. Typical current consumption of the board when the output de-emphasis level is set to OdB (see Table 1) is 50mA when no input signals are applied and 70mA when a signal is applied to the high-speed input of the ISL35111.

#### High Speed Data I/O Interface Connectors

The differential input of the ISL35111 should be connected to a high-speed datastream source, such as a pattern generator. This connection should be made using the input SMA connectors labeled on the board. We recommend using phase (time-delay) matched cables for each differential input to preserve the fidelity of the differential signal. The output SMA connectors provide access to the output differential signal(s) of the ISL35111 and can be connected with phase-matched cables to the DUT channel to be driven. Make sure proper torque (5 in-lbs) is applied to the SMA connectors for reliable measurements and to prevent damage to the connectors.

#### **Output De-Emphasis Control**

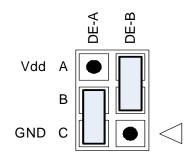

The output driver of on the ISL35111 is capable of providing seven different levels (0 - 6) of de-emphasis. The available output de-emphasis levels range from OdB (DE level = 0) to 4dB (DE level = 6). The output de-emphasis level is set by positioning jumpers on the DE header as illustrated in Figure 2. DE-A and DE-B can each be set to one of three values ( $V_{DD}$ , GND, or Floating). Table 1 gives the jumper positions required to achieve various de-emphasis levels. As an example, Figure 2 depicts the jumper positions that set the output de-emphasis level to 3dB (DE-A = GND and DE-B =  $V_{DD}$ ).

TABLE 1. JUMPER POSITIONS FOR DE SETTINGS

| DEA           | DEB           | DE LEVEL (dB) |

|---------------|---------------|---------------|

| No Jumper     | No Jumper     | 0             |

| No Jumper     | Jumper to GND | 0.6           |

| No Jumper     | Jumper to VDD | 1.1           |

| Jumper to GND | No Jumper     | 1.6           |

| Jumper to GND | Jumper to GND | 2.3           |

| Jumper to GND | Jumper to VDD | 3             |

| Jumper to VDD | No Jumper     | 4             |

FIGURE 2. JUMPER CONFIGURATION FOR 3dB DE-EMPHASIS

### Transmit Disable

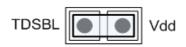

The ISL35111 provides a transmit disable feature, whereby the IC for can be made to enter a low-power standby mode. Entry into this mode is controlled by the TDSBL pin. By using a jumper to tie a given TDSBL pin to  $V_{DD}$  (as shown in Figure 3), the ISL35111 is disabled. While disabled, all internal circuitry of the IC is powered down, and the is incapable of driving any high-speed signal applied to its input. If the TDSBL pin is left floating (no jumper installed), the IC is enabled and is capable of driving high-speed data.

#### FIGURE 3. JUMPER INSTALLED FOR TRANSMIT DISABLE

## **Baseline Performance**

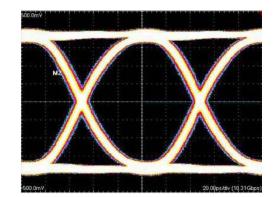

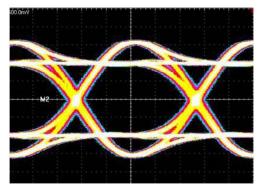

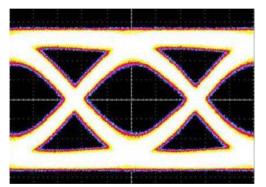

The eye diagrams in Figures 4A through 4C show the typical high-speed performance of the ISL35111DRZ-EVALZ evaluation board. Figure 4A shows the output at 10.3125Gb/s with no output de-emphasis (DE level = 0dB). Figure 4B shows the output at 10.3125Gb/s with maximum output de-emphasis (DE |eve| = 4dB). The output de-emphasis supplied by the ISL35111 can be used to pre-compensate the signal for subsequent frequency-dependent channel loss. Figure 4C shows the eye diagram of a waveform that has been transmitted from the output of the ISL35111 with maximum de-emphasis (DE level = 4dB) across a 22-inch long trace on an FR408 circuit board. The trace loss at 5GHz is approximately -8dB. The open eye diagram in Figure 4C illustrates the channel equalization capabilities of the ISL35111's output de-emphasis feature.

FIGURE 4A. 10.3125Gb/s EYE DIAGRAM AT ISL35411DRZ-EVALZ EVALUATION BOARD OUTPUT (OUTPUT LEVEL = 0dB)

FIGURE 4B. 10.3125Gb/s EYE DIAGRAM AT ISL35411DRZ-EVALZ EVALUATION BOARD OUTPUT (OUTPUT LEVEL = 4dB)

FIGURE 4C. 10.3125Gb/s EYE DIAGRAM AFTER TRANSMISSION FROM ISL35411 ACROSS 22-in. FR408 TRACE (OUTPUT DE-LEVEL = 4dB)

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com

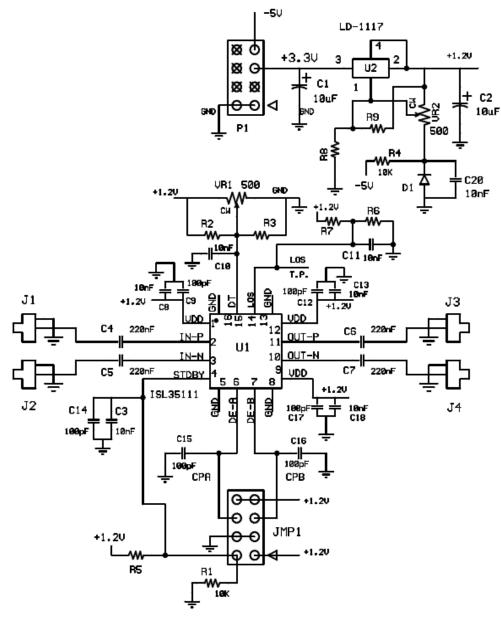

### **Schematic**

The ISL35111 evaluation board schematic is shown in Figure 5.

FIGURE 5. ISL35111 EVALUATION BOARD SCHEMATIC

4